# GOVERNMENT OF TAMILNADU DIRECTORATE OF TECHNICAL EDUCATION CHENNAI – 600 025

### STATE PROJECT COORDINATION UNIT

### **Diploma in Computer Engineering**

Course Code: 1052 M – Scheme

### e-TEXTBOOK

on

# **Basics of Electrical and Electronics Engineering**

for

III Semester Dip. In Comp. Engg.

### **Convener for Computer Engineering Discipline:**

### Mr.D. Arulselvan

HOD / Post Diploma in Computer Applications Thiagarajar Polytechnic College, Salem – 636 005

### **Team Members :**

### Mr.K.Rajan (4th Unit)

Lecturer (Sel.Gr) / Electrical and Electronics Engg Muthiah Polytechnic College Annamalai Nagar, Chidambaram – 608 002.

### Mr.F.Arumai Nathan (1st and 2nd units)

Lecturer (Sel.Gr) / Electrical and Electronics Engg Muthiah Polytechnic College Annamalai Nagar, Chidambaram – 608 002

#### Mr.B.Krishnakumar, (3rd and 5th Units)

HOD / Computer Engg Arasan Ganesan Polytechnic College, Sivakasi – 626130

### Validated By

**R. Rajesh, Lecturer** TPEVR Govt. Polytechnic College, Vellore – 2

# UNIT I. AC FUNDAMENTALS, BATTERIES AND UPS

- > **OBJECTIVES:**

- Understand the AC fundamentals

- Understand the basic terms of AC

- > Know about Batteries

- Battery charging method

- > Understand the working principle of UPS

### **1.1 AC FUNDAMENTALS**

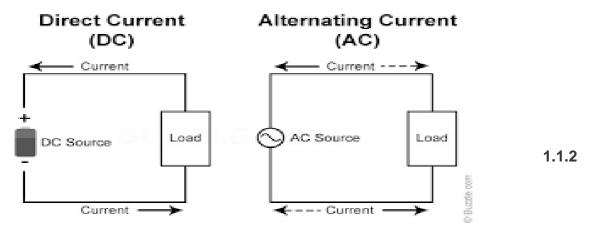

### 1.1.1 DIFFERENCE BETWEEN AC AND DC

### AC current

Alternating current is defined as the flow of charge that changes direction periodically. The result obtained will be, the voltage level also reverses along with the current.

A.C, current and voltages are varying in magnitude and polarity.

### **DC current**

By D.C, we mean current and voltages have a fixed polarity and constant Magnitude.

Direct current (DC) is a flow of electrical charge carriers that always takes place in the same direction.

### ADVANTAGES OF AC OVER DC

We all know that we got ac supply in our homes and we got this supply by transmitting ac over long distances.

Electric energy is generated and used is AC because it offers much advantages then DC. The few are listed below:-

### **ADVANTAGES**

1. AC can be transmitted using step up transformers but direct current or dc Cannot be transmitted by this method.

- 2. The ac is easy to generate than dc.

- 3. It is cheaper to generate ac than dc.

- 4. The ac generators have higher efficiency than dc.

- 5. The loss of energy during transmission is negligible for ac.

- 6. The ac can be easily converted into dc.

- 7. The variation of ac can easily be done using transformers either step up or step down.

- 8. AC can be generated at high voltages, but DC cannot be generated at high

Voltages because sparking starts at the commentator at high voltage, due to which commutator gets damaged.

- 9. The magnitude of current can be reduced by using an inductance or a conductor Without any appreciable loss of energy

- 10. A.C. machines are simple, robust and do not require much attention for their Repairs and maintenance during their use.

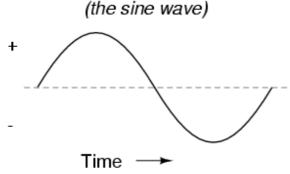

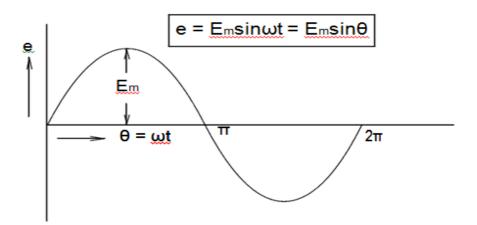

#### 1.1.3 WAVEFORM OF SINUSOIDAL A.C.CYCLE.

When an alternator produces AC voltage, the voltage switches polarity over time, but does so in a very particular manner. When graphed over time, the "wave" traced by this voltage of alternating polarity from an alternator takes on a distinct shape, known as a Sine wave: Figure below Graph of AC voltage over time (the sine wave).

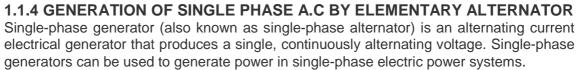

# Fig 1.Elementary generator is an example of single-phase generators with two poles

A synchronous generator is an electrical machine producing alternating emf (Electromotive force or voltage) of constant frequency. The basic principles involved in the production of emf and the constructional details of the generators are:

\* Faraday discovered that an emf can be induced (or generated) due to relative motion between a magnetic field and a conductor of electricity.

\*This voltage was termed as the induced emf since the emf is produced only due to motion between the conductor and the magnetic field without actual physical contact between them.

\*The magnetic field is produced by the two fixed poles one being the North Pole from which the magnetic flux lines emerge and enter into the other pole known as the South Pole.

\*It was found that the magnitude of the voltage induced in the conductor is proportional to the rate of change of flux lines linking the conductor.

Mathematically it is given as

$e = d\phi/dt \approx \phi/t$  volts -----(1)

\*The above Eqn. 1 holds good only when the magnetic circuit is physically the same at the end as at the beginning and also during the period of change of flux linkages as well.

\*In practical rotating machinery, however the change of flux linking each individual conductor during rotation (of either the conductors or the poles) is not clearly defined or cannot be easily measured.

\*It is therefore more convenient to express this rate of change of flux in terms of an average flux density (assumed constant) and the relative velocity between this field and a single conductor moving through it.

\*For the conductor of active length I moving with a velocity of v in a magnetic field of flux density B, as shown in Fig. 1, the instantaneous induced emf is expressed as,  $e = Blv \quad Volts(2)$

### Where

B= flux density in Tesla (Wb/m2), I = active conductor length (m)

v = relative linear velocity between the conductor and the field (m/s).

\* Thus the instantaneous voltage e and the average value E of the induced emf are

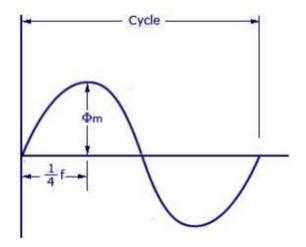

Figure 2: Sinusoidal voltage waveform

### 1.1.5 Definition

• A Sine Wave Waveform

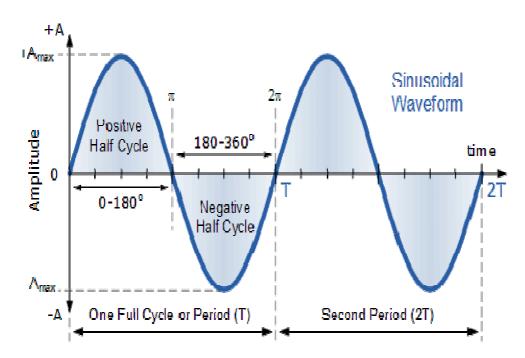

### CYCLE:

A set of positive and negative half cycle called one cycle.

Positive half cycle- 0-180°

Negative half cycle- 180-360°

One cycle=0-360°

### PERIOD:

This is the length of time in seconds that the waveform takes to repeat itself from start to finish. This value can also be called the *Periodic Time*, (T) of the waveform for sine waves, or the *Pulse Width* for square waves.

- Units of periodic time, (T) include: Seconds (s), milliseconds (ms) and microseconds (µs).

- For sine wave waveforms only, we can also express the periodic time of the waveform in either degrees or radians, as one full cycle is equal to  $360^{\circ}$  (T =  $360^{\circ}$ ) or in Radians as 2pi,  $2\pi$  (T =  $2\pi$ ), then we can say that  $2\pi$  radians =  $360^{\circ}$  (Remember this!).

### FREQUENCY:

This is the number of times the waveform repeats itself within a one second time period.

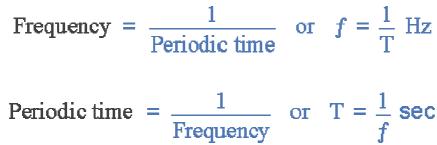

\*Frequency is the reciprocal of the time period, (f = 1/T) with the standard unit of frequency being the *Hertz*, (Hz).

- We now know that the time it takes for electrical waveforms to repeat themselves is known as the periodic time or period which represents a fixed amount of time. If we take the reciprocal of the period, (1/T) we end up with a value that denotes the number of times a period or cycle repeats itself in one second or cycles per second, and this is commonly known as **Frequency** with units of **Hertz**, (Hz). Then Hertz can also be defined as "cycles per second" (cps) and 1Hz is exactly equal to 1 cycle per second.

- Both period and frequency are mathematical reciprocals of each other and as the periodic time of the waveform decreases, its frequency increases and vice versa with the relationship between *Periodic time* and *Frequency* given as.

- Relationship between Frequency and Periodic Time

Where: *f* is in Hertz and T is in Seconds.

One Hertz is exactly equal to one cycle per second, but one hertz is a very small unit so prefixes are used that denote the order of magnitude of the waveform such as kHz, MHz and even GHz

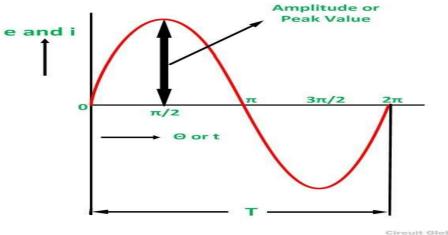

### **AMPLITUDE:**

This is the magnitude or intensity of the signal waveform measured in volts or amps.

### **PEAK VALUE**

**Definition:** The maximum value attained by an alternating quantity during one cycle is called its Peak value.

It is also known as the maximum value or amplitude or crest value.

The sinusoidal alternating quantity obtains its peak value at 90 degrees as shown in the figure below. The peak values of alternating voltage and current is represented by E<sub>m</sub> and I<sub>m</sub> respectively.

Circuit Globe

### **AVERAGE VALUE**

Definition: The average of all the instantaneous values of an alternating voltage and currents over one complete cycle is called Average Value.

If we consider symmetrical waves like sinusoidal current or voltage waveform, the positive half

Cycle will be exactly equal to negative half cycle. Therefore, the average value over a **complete**

#### cycle will be zero.

The work is done by both, positive and negative cycle and hence the average value is determined without considering the signs.

So the only positive half cycle is considered to determine the average value of alternating quantities of sinusoidal waves. Let us take an example to understand it.

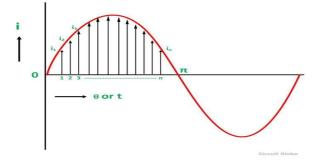

Divide the positive half cycle into (*n*) number of equal parts as shown in the above figure

Let  $i_1$ ,  $i_2$ ,  $i_3$ .....  $i_n$  be the mid ordinates

The Average value of current  $I_{av}$  = mean of the mid ordinates

$I_{av} = \frac{i_1 + i_2 + i_3 + \dots + i_n}{n} = \frac{\text{Area of alternation}}{\text{Base}}$

For Ac

Vavg=0.637\*Vm

lavg=0.637\*lm

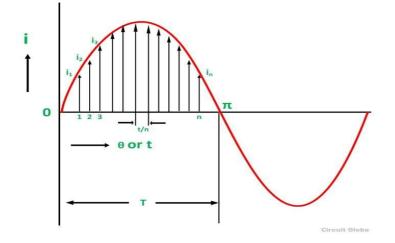

### R.M.S Value (Root Mean Square)

**Definition:** That steady current which, when flows through a resistor of known resistance for a given period of time than as a result the same quantity of heat is produced by the alternating current when flows through the same resistor for the same period of time is

called **R.M.S** or effective value of the alternating current. In other words, the R.M.S value is defined as the square root of means of squares of instantaneous values.

Let I be the alternating current flowing through a resistor R for time t seconds, which produces the same amount of heat as produced by the direct current ( $I_{eff}$ ). The base of one alteration is divided into n equal parts so that each interval is of t/n seconds as shown in the figure below

Let i<sub>1</sub>, i<sub>2</sub>, i<sub>3</sub>,.....in be the mid ordinates

$I_{eff}$  = square root of mean of squares of instantaneous values = R.M.S value

Root Mean Square is the actual value of an alternating quantity which tells us an energy transfer capability of an AC source. The ammeter records the RMS value of alternating current and voltmeter record's the root mean square (R.M.S) value of alternating voltage. The domestic single phase AC supply is 230 V, 50 hertz, where 230 V is the R.M.S value of alternating voltage.

#### For ac

### Vrms (or) Veff (or) V=0.707\*Vm

#### Irms (or) leff (or) I=0.707\*Im

#### 1.1.6 Define Peak factor and Form factor

There is a relation between the peak value, the average value, and the root means square (R.M.S) value of an alternating quantity. Therefore, to express the relationship between all these three quantities, the two factors are used, namely as Peak Factor and Form Factor

#### PEAK FACTOR

#### **Definition:**

**Peak Factor** is defined as the ratio of maximum value to the R.M.S value of an alternating quantity.

The alternating quantities can be voltage or current. The maximum value is the peak value or the crest value or the amplitude of the voltage or current and the root mean square value is the amount of heat produced by the alternating current will be same when the direct supply of current is passed through the same resistance in the same given time.

Mathematically it is expressed as

Peak Factor =

$$\frac{I_m}{I_{r.m.s}}$$

or  $\frac{E_m}{E_{r.m.s}}$

Where,

$I_m$  and  $E_m$  are the maximum value of the current and the voltage respectively, and  $I_{r.m.s}$  and  $E_{r.m.s}$  are the root mean square value of the alternating current and the voltage respectively.

#### The value of Peak Factor is 1.4142

#### FORM FACTOR

**Definition:** The ratio of the root mean square value to the average value of an alternating quantity (current or voltage) is called **Form Factor.** The average of all the instantaneous values of current and voltage over one complete cycle is known as the average value of the alternating quantities. Mathematically, it is expressed as

Form Factor =

$$\frac{I_{r.m.s}}{I_{av}}$$

or  $\frac{E_{r.m.s}}{E_{av}}$

$I_{r.m.s}$  and  $E_{r.m.s}$  are the roots mean square value of the current and the voltage respectively, and  $I_{av}$  and  $E_{av}$  are the average value of the alternating current and the voltage respectively.

### The value of Form Factor is 1.11

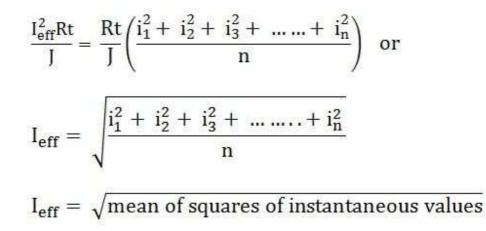

#### **1.1.7. CONCEPT OF PHASE**

**Phase** denotes the particular point in the cycle of a waveform, measured as an angle in degrees

#### PHASE DIFFERENCE AND PHASE ANGLE

We saw that the Sinusoidal Waveform (Sine Wave) is an alternating quantity that can be presented graphically in the time domain along an horizontal zero axis.

We also saw that as an alternating quantity, sine waves have a positive maximum value at time  $\pi/2$ , a negative maximum value at time  $3\pi/2$ , with zero values occurring along the baseline at 0,  $\pi$  and  $2\pi$ .

However, not all sinusoidal waveforms will pass exactly through the zero axis point at the same time, but may be "shifted" to the right or to the left of  $0^{\circ}$  by some value when compared to another sine wave.

#### **Phase Difference Equation**

$A_{(t)} = A_{max} \times sin(\omega t \pm \Phi)$

- Where:

- A<sub>m</sub> is the amplitude of the waveform.

- ωt is the angular frequency of the waveform in radian/sec.

- Φ (phi) is the **phase angle** in degrees or radians that the waveform has shifted either left or right from the reference point.

For example, comparing a voltage waveform to that of a current waveform. This then produces an angular shift or **Phase Difference** between the two sinusoidal waveforms. Any sine wave that does not pass through zero at t = 0 has a phase shift.

The **phase difference** or phase shift as it is also called of a Sinusoidal Waveform is the angle  $\Phi$  (Greek letter Phi), in degrees or radians that the waveform has shifted from a certain reference point along the horizontal zero axis. In other words phase shift is the

lateral difference between two or more waveforms along a common axis and sinusoidal waveforms of the same frequency can have a phase difference.

Phase Angle: The angle difference between zero crossing points of two wave form.

### Phase Relationship of a Sinusoidal Waveform

### 1.1.8 Single phase and 3 phase

### **DEFINITION OF SINGLE PHASE**

The single phase requires two wires for completing the circuit, i.e., the conductor and the neutral. The conductor carries the current and the neutral is the return path of the current. The single phase supplies the voltage up to 230 volts. It is mostly used for running the small appliances like a fan, cooler, grinder, heater, etc.

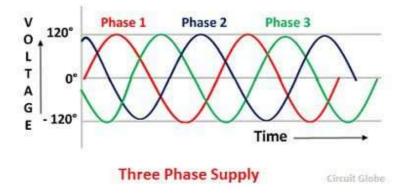

**Definition of Three Phase**

The three phase system consist four wires, three conductors and one neutral. The conductors are out of phase and space 120° apart from each other. The three phase system is also used as a single phase system. For the low load, one phase and neutral can be taken from the three phase supply.

The three phase supply is continuous and never completely drops to zero. In three phase system power can be drawn either in a star or delta configuration. The star connection is used for long distance transmission because it has neutral for the fault current.

### Key Differences between Single Phase and Three Phase

- 1. In single phase supply, the power flows through one conductor whereas the three phase supply consists three conductors for power supply.

- 2. The single phase supply requires two wires (one phase and one neutral) for completing the circuit. The three phases requires three phase wires and one neutral wire for completing the circuit.

- 3. The single phase supplies the voltage up to 230V whereas the three phase supply carries the voltage up to 415V.

- 4. The maximum power is transferred through three phases as compared to single phase supply.

- 5. The single phase has two wires which makes the network simple whereas the three phase network is complicated as it consists four wires.

- 6. The single phase system has only one phase wire, and if the fault occurs on the network, then the power supply completely fails. But in three phase system the network has three phases, and if the fault occurs on any one of the phases, the other two will continuously supply the power.

- 7. The efficiency of the single phase supply is less as compared to three phase supply. Because the three phase supply requires less conductor as compared to single phase supply for the equivalent circuit.

- 8. The single phase supply requires more maintenance and become costly as compared to three phase supply.

- 9. The single phase supply is mostly used in the house and for running the small loads. The three phase supply is used in large industries and for running the heavy loads.

The star connection of the three phases allows the use of two different voltages (i.e., the 230 volts and the 415 volts). The 230V is supplied by using the one phase and one neutral wire, and the three phases is supply between any two phases.

### 1.1.9 Meaning of lagging and leading sine wave

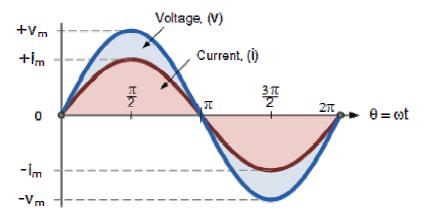

#### Two Sinusoidal Waveforms – "in-phase"

Both voltage and current crossing zero at 180° or  $\pi$ . Hence V and I are in phase or phase difference between V and I is zero.

i.e. Phase angle between V and I=0.

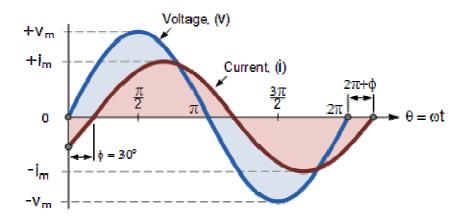

### Phase Difference of a Sinusoidal Waveform

Here V crossing zero at 180° or  $\pi$ .

But I crossing zero after 180. i.e. 180+30 or  $\pi$ +30.

Hence I lagging V by 30° or V leading I by 30°

#### Phase angle 30°

. .

1.1.10 ADVANTAGES OF THREE PHASE OVER SINGLE PHASE

- 1. From power wave forms shown in figure (C) and (D) above it is clear that in 3-phase system, the instantaneous power is always constant over the cycle results in smooth and vibration free operation of machine. Whereas in 1-ø system the instantaneous power is pulsating hence change over the cycle, which leads to vibrations in machines.

- 2. Power to weight ratio of three phase induction motor is high as compare to single phase induction motor. Means for same amount of Mechanical Power, the size of three phase induction motor is small as compare to single phase induction motor. Hence, the overall cost of induction motor is reduced. Moreover, due to reduction in weight, transportation and installation of induction motor become convenient and less space is required to accommodate the induction motor.

- 3. 3-phase induction motor is self-started as the magnetic flux produced by 3-phase supply is rotating in nature with constant magnitude. Whereas 1-ø induction motor is not self-started as the magnetic flux produced by 1-ø supply is pulsating in nature. Hence, we have to make some arrangement to make the 1-ø induction motor self-started which further increases the cost of 1-ø induction motor.

- 4. 3-phase motor is having better power factor and efficiency as compare to 1-ø motor.

- 5. Power to weight ratio of 3-phase transformer is high as compare to 1-ø transformer. Means for same amount of Electric Power, the size of 3-phase transformer is small as compared to 1-ø transformer. Hence, the overall cost of transformer is reduced. Moreover, due to reduction in weight, transportation and installation of transformer become convenient and less space is required to accommodate the transformer.

- 6. If fault occurs in any winding of 3-phase transformer, the rest of two winding can be used in open delta to serve the 3-phase load which is not possible in 1-ø transformer. This ability of 3-phase transformer further increases the reliability of 3-phase transformer.

- 7. A 3-phase system can be used to feed a 1-ø load, whereas vice-versa is not possible.

- 8. DC rectified from 3-phase supply is having the ripple factor 4% and DC rectified from 1-ø supply is having the ripple factor 48.2%. Mean DC rectified from 3-ø supply contains less ripples as compare to DC rectified from 1-ø supply. Hence the requirement of filter is reduced for DC rectified from 3-phase supply. Which reduce the overall cost of converter.

From above it is clear the 3-phase system is more economical, efficient, reliable and convenient as compared to 1-ø system.

### **1.2 BATTERIES**

### **1.2.1 Classification of Cells or Batteries**

The Nickel Cadmium (NiCd) battery. The Nickel-Metal Hydride (NiMH) battery. The Lead Acid battery. The Lithium Ion battery.

The Lithium Polymer battery.

A primary cell or battery is one that cannot easily be *recharged* after one use, and are discarded following discharge. Most primary cells utilize electrolytes that are contained within absorbent material or a *separator* (i.e. no free or liquid electrolyte), and are thus termed dry cells.

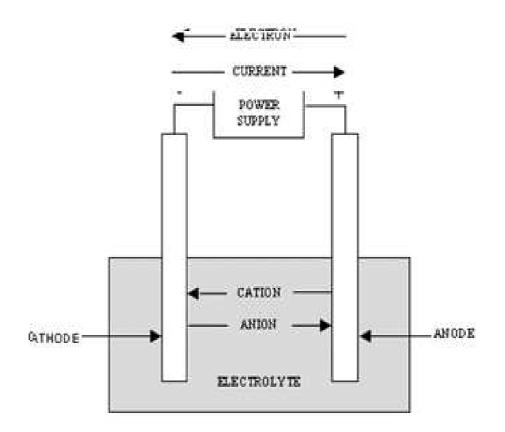

A secondary cell or battery is one that can be electrically recharged after use to their original pre-discharge condition, by passing current through the circuit in the opposite direction to the current during discharge.

The following graphic evidences the recharging process

Figure 3: Recharging a Cell

### **1.2.2 CONSTRUCTION OF LEAD ACID CELL**

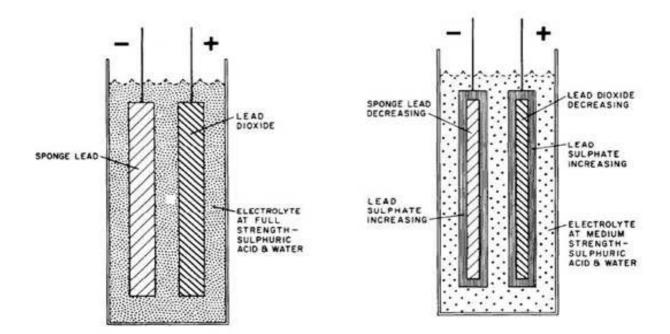

In the fully charged state, the negative plate consists of lead, and the positive plate lead dioxide, with the electrolyte of concentrated sulfuric acid. Overcharging with high charging voltages generates oxygen and hydrogen gas by electrolysis of water, which is lost to the cell.

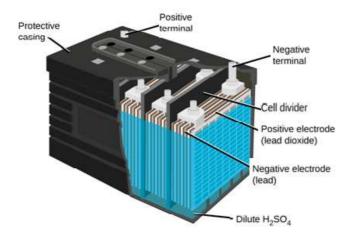

### LEAD ACID BATTERY

In lead acid battery there is a group of cells and in each cell there is one group of positive plates and one group of negative plates. The **positive plates** are made of lead peroxide **(PbO2)** and **negative plate** is made of **spongy lead**. Thus for identification the **positive plate** as the color of **dark brown**, whereas the **negative plate** as the **color of light salty**.

### MAIN PARTS OF LEAD ACID BATTERY

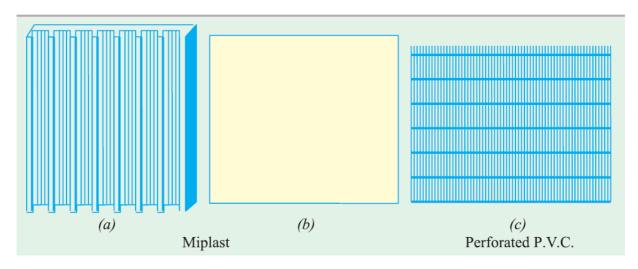

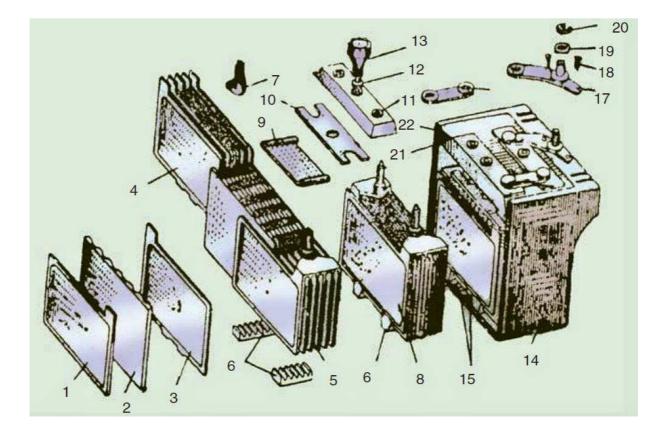

A battery consists of a number of cells and each cell of the battery-consists of (a) positive and negative plates (b) separators and (c) electrolyte, all contained in one of the many compartments of the battery container. Different parts of a lead-acid battery are as under: (I)PLATES: A plate consists of a lattice type of grid of cast antimonial lead alloy which is covered with active material. The grid not only serves as a support for the fragile active material but also conducts electric current. Grids for the positive and negative plates are often of the same design although negative plate grids are made somewhat lighter. (II) <u>SEPARATORS</u>: These are thin sheets of a porous material placed between the positive and negative plates for preventing contact between them and thus avoiding internal short-circuiting of the battery. A separator must, however, be sufficiently porous to allow diffusion or circulation of electrolyte between the plates. These are made of especially-treated cedar wood, glass wool mat, micro porous rubber (mipor), micro porous plastics (plastipore, miplast) and perforated PVC, as shown in Figure In addition to good porosity, a separator must possess high electrical resistance and mechanical strength.

(III)ELECTROLYTE: It is dilute sulphuric acid which fills the cell compartment to immerse the plates completely.

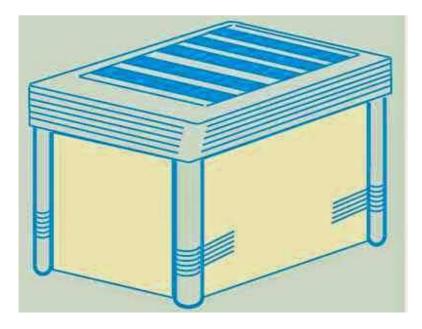

**(IV)** <u>CONTAINER</u>: It may be made of vulcanized rubber or molded hard rubber (ebonite), molded plastic, ceramics, glass or celluloid. The vulcanized rubber containers are used for car service, while glass containers are superior for lighting plants and wireless sets. Celluloid containers are mostly used for portbable wireless set batteries. A single monoblock type container with 6 compartments generally used for starting batteries is shown in Figure.

(V) <u>BOTTOM GROOVED SUPPORT BLOCKS</u>: These are raised ribs, either fitted in the bottom of the container or made with the container itself. Their function is to support the plates and hold them in position and at the same time protect them from short-circuits that would otherwise occur as a result of fall of the active material from the plates onto the bottom of the container.

(VI) <u>CONNECTING BAR</u>: It is the lead alloy link which joins the cells together in series connecting the positive pillar of one cell to the negative pillar of the next one.

(VII) <u>TERMINAL POST OR PILLAR</u>: It is the upward extension from each connecting bar which passes through the cell cover for cable connections to the outside circuits. For easy identification, the negative terminal post is smaller in diameter than the positive terminal post.

(VIII) <u>VENT PLUGS OR FILLER CAPS</u>: These are made of polystyrene or rubber and are usually screwed in the cover. Their function is to prevent escape of electrolyte but allow the free exit of the gas. These can be easily removed for topping up or taking hydrometer readings.

(IX) <u>EXTERNAL CONNECTING STRAPS</u>: These are the antimonial lead alloy flat bars which connect the positive terminal post of one cell to the negative of the next across the top of the cover. These are of very solid construction especially in starting batteries because they have to carry very heavy currents.

- 1. -ve plate

- 2. Separator

- 3. + Ve plate.

- 4. + ve group

- 5. -ve group

- 6. -ve group grooved support block

- 7. Lug

- 8. Plate group

- 9. Guard screen

- 10. Guard plate

- 11. Cell cover

- 12. Plug washer

- 13. Vent plug

- 14. Mono-block jar

- 15. Supporting prisms of + ve group

- 16. Inter-cell connector

- 17. Terminal lug

- 18. Screw

- 19. Washer

- 20. Nut

- 21. Rubber packing

- 22. Sealing compound.

### **1.2.3METHODES OF CHARGING**

### **BASIC CHARGING METHODS**

Charging Methods charging is a process of supplying direct current to the battery so as to convert it back into chemical state at high energy level, capable of delivering electric power.

Charging voltages have a significant effect on battery longevity. Some cells may deteriorate faster than others during operations. Deteriorated cells reduce the output voltage of the battery, and affect the usability and reliability of the circuit.

There are varieties of charging methods which can be used to charge sealed lead acid battery.

By controlling the charging process, these methods can be classified into some basic categories which are

#### (i) constant-voltage,

- (ii) constant-current,

- (iii) tapered-current

- (iv) Combination charge systems..

### **1.2.3.1CONSTANT VOLTAGE**

A constant voltage charger is basically a DC power supply which in its simplest form may consist of a step down transformer from the mains with a rectifier to provide the DC voltage to charge the battery.

Such simple designs are often found in cheap car battery chargers. The lead-acid cells used for cars and backup power systems typically use constant voltage chargers. In addition, lithium-ion cells often use constant voltage systems, although these usually are more complex with added circuitry to protect both the batteries and the user safety.

Constant voltage charging is a methods use to restore the battery to a fully charge condition in short period of time.

This type of charging must has a very stable output voltage and high current capacity, as extremely large currents are allowed to flow in the initial stage of charge, where the battery voltage is low.

However, this type of charging method is not practical because the requirement of a high current capacity, results in high cost.

The heat generation in the battery is also high because of the high current flow in the battery causing the battery life to be short.

Generally, constant voltage charger has a device to limit initial current. This can be accomplished by a constant current regulator, or by designing the overall impedance of the circuit.

Constant voltage charger is effectively to charge the battery at short period of time, as during the final stage of charge, the current automatically decreases and the water decomposition will be minimized.

### **1.2.3.2CONSTANT CURRENT**

Constant current charging is a method that is commonly uses for charging lead acid battery.

The advantage of using this method is it easy to determine the amount of capacity (amp hrs) supplied during charging process.

Besides that, there is no need for temperature compensation which is required in constant voltage systems.

Usually, at high-rate of charging, the battery voltage rises excessively and the water decomposes, causing heat generation at the final stage of the charge, thus, damaging the battery.

However, the constant current method relatively kept a low rate of charging process and charging time is not critical.

The constant current methods may be used as refreshing charge when many batteries is being charge at one time, as this method easily determine the amount of charge returned to the battery.

It is not recommended to use constant current charging as refreshing the battery because it will shorten the battery life.

Constant current chargers vary the voltage they apply to the battery to maintain a constant current flow, switching off when the voltage reaches the level of a full charge. This design is usually used for nickel-cadmium and nickel-metal hydride cells or batteries.

#### 1.2.3.3TAPER CURRENT

Tapered current charging is simple and relatively inexpensive method.

This charging method requires circuit with power transformer, rectifiers and a suitable resistance for limiting current.

In this method, the charging current drops gradually as the charging proceeds. If the impedance of the circuit is low, a step current slope can be obtained.

This type for charge is generally considered to be unsuitable for charging sealed lead acid batteries because the charging current will vary with fluctuation of line voltage as well as changes in battery voltage.

These effects, however, can be minimized by using a power transformer with a secondary voltage which is considerably higher than the battery voltage and a suitably high resistance in the circuit for current limiting.

This type of charger will perform similar to a constant current charger, and can be utilized instead of a constant current charger for industrial uses; not only for recharging many batteries at one time, but also as a trickle charging system.

### 1.2.3. Combination Charging (Two-Step)

A combination charging uses two types of charging. It's called a —Two-rate or —Two-step charging.

A variety of couples can be made, such as constant – current/constant current, constant-voltage/constant-current and so on .

In general the first step uses a quick or fast charge mode, and the second uses a low charge current.

The switching from the first step to the second can be carried out by many different methods such as battery voltage sensing, a time control, charge current sensing and many more.

### 1.2.4 CARE AND MAINTENANCE OF LEAD ACID BATTERY REGULAR INSPECTION AND MAINTENANCE.

Regular testing and inspection will help to maximize battery life. A routine inspection at least once a month is recommended to maintain optimum performance.

1. Ensure the battery top is clean and dry, free of dirt and grime. A dirty battery can discharge across the grime on top of the battery casing.

2. Inspect the terminals, screws, clamps and cables for breakage, damage or loose connections. These should be clean, tight and free of corrosion.

3. Apply a thin coating of high temperature grease to posts and cable connections for added protection.

4. Inspect the battery case for obvious signs of physical damage or war page. This usually indicates the battery has overheated or has been overcharged.

5. If the battery is maintainable, check electrolyte levels to ensure that fluid levels are over the top of battery plates. If necessary top up using distilled or demine rallied water. Never top up fluid levels with acid.

6. Test the battery using either a hydrometer or voltmeter and charge if necessary.

- 7. Keep vent caps in place.

- 8. Charge in well ventilated area.

- 9 .Apply petroleum products or Vaseline (both are use corrosion precaution)

- 10. Watering

Watering is the single most important step in maintaining a flooded lead acid battery; a requirement that is all too often neglected. The frequency of watering depends on usage, charge method and operating temperature. Over-charging also leads to water

#### consumption.

A new battery should be checked every few weeks to estimate the watering requirement. This assures that the top of the plates are never exposed. A naked plate will sustain irreversible damage through oxidation, leading to reduced capacity and lower performance.

If low on electrolyte, immediately fill the battery with distilled or de-ionized water. Tap water may be acceptable in some regions. Do not fill to the correct level before charging as this could cause an overflow during charging. Always top up to the desired level after charging. Never add electrolyte as this would upset the specific gravity and promote corrosion. Watering systems eliminate low electrolyte levels by automatically adding the right amount of water.

#### 11. Specific gravity.

The specific gravity of the electrolyte may be permanently decreased due to ageing effects. This problem is generally found in old battery cells. This is mainly due to,

- 1. Action of sediment-at the bottom of the cell container.

- 2. Due to loss of acid by spray during charging.

- 3. Inadequate treatment after the removal short circuit.

- 4. Due to excessive sulphation on the plates.

If the lowering of specific gravity is not due to sulphation or short circuit, concentrated sulfuric acid may be added to restore normal value of specific gravity.

A short circuit may occur between the positive and negative plates either due to treeing or due to buckling of the plates.

Treeing is usually due to excessive gassing which tends to loosen the active materials from the plates. The particles of active materials fall into the electrolyte and may accumulate on the negative plates in such a way as to bridge the space between the positive and negative plates. This treeing can be removed by the use of scaling stick made of ebonite. By this stick it is possible to explore the space between these two types of plates of a cell and to remove loose materials or treeing.

If the short circuit is due to buckling of plates, this can be removed by inserting additional separator or by removing and straightening the plates mechanically.

After removing of short circuit, care should be taken to restore the specific gravity of the electrolyte to normal by constant charging by high current.

#### **1.2.5Indications of a fully charge battery** There are two measures,

- (I) cell voltage

- (ii) Specific gravity of the electrolyte.

\*Cell voltage is the simplest to measure. For most automotive, flooded cell

(Having liquid electrolyte) batteries, 12.6 volts are considered full charge,

Although it is typical to have 13 volts or a bit over.

\*The specific gravity of a fully charged battery, measured with a hydrometer, is 1.265.

\*If the charger has a ammeter on it then it should show close to zero which means the battery is no longer pulling any current from the charger which would mean the battery is fully charged.

\*If it has only a voltmeter then it should show 12.5-13.5 vdc.

\*When a battery is fully charged, the amount of sulfuric acid mixed with the

water is sufficient to give a specific gravity of about 1.3.

\* In the fully charged condition the active material of the positive plate is lead Dioxide as the color of **dark brown**, whereas the **negative plate** sponge lead as the **Color of light salty**, indicated electrolyte is a solution of sulfuric acid and water that normally varies in specific gravity from 1.275 to 1.295.

\*The combination produces a voltage of approximately 2 volts on open circuit.

\*A fully charged cell should normally have an on-charge voltage of from 2.45 to 2.7

### 1.2.6Sealed or maintenance-free batteries

Sealed or maintenance free Batteries have the following features: -

i) Maintenance-free, no water adding required

ii) Sealed valve-regulated, spill proof and leak proof

iii) Using unilateralism exhaust (safe vent valve) design on the battery cover When the battery internal pressure have been up to the specifically value, the safe vent valve will open automatically, and will close after the pressure has been discharged, which can prevent the air to enter into battery

They are designed in such a way as to recover a large portion of the electrolyte that is normally lost through gassing of a normal wet cell.

Even so, these batteries will lose electrolyte over time, causing premature failure due to overcharging.

### Use

They are suitable to be used

- i) Standby or cyclical

- ii) Security sector (alarm),

- iii) Electronically devices,

- iv) Telephone exchange and UPS.

### 1.3 UPS

The ever increasing importance of computers in industry and commerce will increase the need for quality, high stability and interruption free power supplies.

A clean ac power source is the fundamental to the operation of most sensitive electronic equipment, and many new and sophisticated circuits are designed to overcome the effects of disturbances normally found in the mains ac supply.

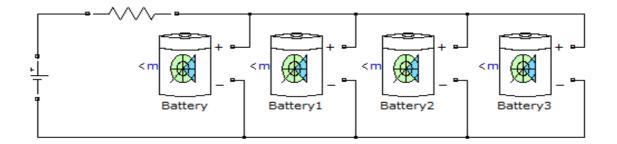

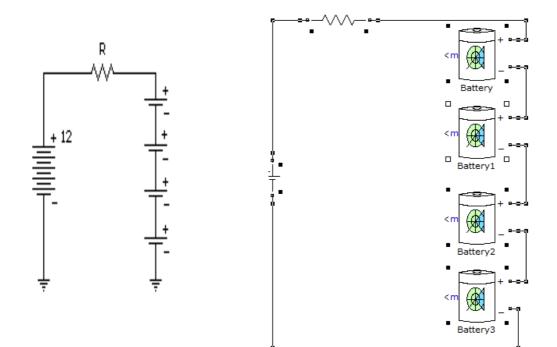

In order to protect a sensitive system from power losses and blackouts, an alternative power source is required that can switch into operation immediately when disruption occurs. Un interruptible power supply (UPS) is just such an alternative source. A UPS generally consists of a rectifier, battery charger, a battery bank and inverter circuit which converts the commercial ac input into dc suitable for input to the battery bank and the inverter. The rectifier should have its input protected and should be capable of supplying power to the inverter when the commercial supply is either slightly below the normal voltage or slightly above.

#### What is UPS?

An uninterruptible power supply (**UPS**) is a device that allows a computer to keep running for at least a short time when the primary power source is lost. It also provides protection from power surges.

#### **1.3.1NEED FOR UPS**

An Uninterruptible Power Supply (UPS) is used to protect critical loads from mains supply problems, including spikes, voltage dips, and fluctuations and complete power failures using a dedicated battery. A UPS system can also be used to 'bridge the gap' whilst a standby generator is started and synchronized.

### **1.3.2Uninterruptible Power Supply Systems.**

There are two distinct types of uninterrupted power supplies, namely,

### Definition

#### **On-line UPS**

In the on-line UPS, whether the mains power is on or off, the battery operated inverter is on all the time and supplies the ac output voltage. When the mains power supply goes off, the UPS will be on only until the battery gets discharged. When the main power resumes, the battery will get charged again.

**UPS.** (Uninterruptible Power Supply) A device that provides battery backup when the electrical power enough to power down the computer in an orderly manner, while larger systems have enough battery for several hours. fails or drops to an unacceptable voltage level. Small UPS systems provide power for a few minutes

### Off-line UPS

In off-line UPS and electronic generators, the inverter is off when the mains power is present and the output voltage derived directly from the mains is the same as the mains supply voltage. The inverter turns on only when the mains supply goes off.

Standby and Line Interactive. A standby UPS, also called an "offline UPS," is the most common type of UPS found in a computer or office supply store. It draws current from the AC outlet and switches to battery within a few milliseconds after detecting a power failure.

### 1.3.3Block Diagram

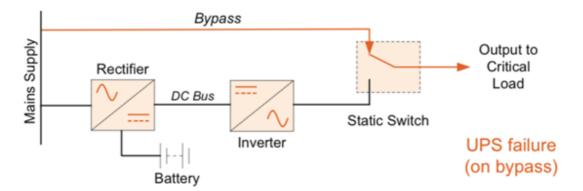

### **Online UPS**

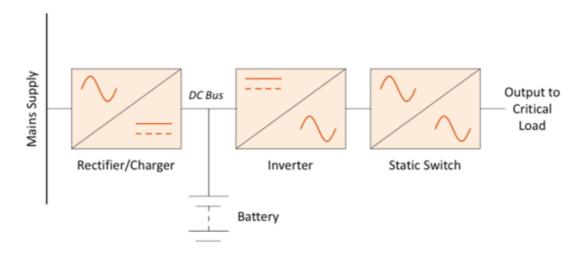

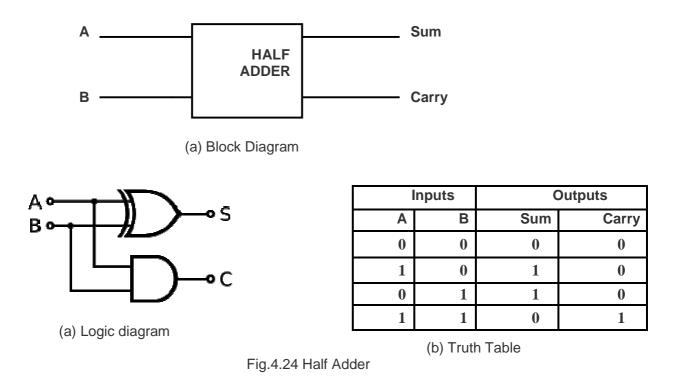

An online UPS comprises four main parts: A rectifier/charger block, a battery, an inverter and a static switch. To see how these components fit together, have a look at the following simple block diagram.

### 1.3.4Explanation of each block

**Rectifier/Charger block**– Although I've listed them together, the rectifier and charger can either be separate modules or combined as a single power block. They perform the same function either way, so for the sake of simplicity they are displayed in our block diagram as a single component.

The function of this combined power block is to take AC (Alternating Current) power from the mains, and convert it to DC (Direct Current) power, which is required to charge the battery. From there the charger directs power to the battery in order to maintain charge, and the rectifier provides a stable DC current directly to the inverter, all via the DC Bus.

During times of power outage or fluctuation (typically outside +10% to -20% of normal) the charger shuts down, and the battery provides DC power to the inverter instead.

**Battery**– most UPS systems utilize lead-acid batteries.

**Inverter**– The inverter provides the second half of our double conversion process, by converting DC power from the rectifier/battery back to AC power. We needed DC power to charge the battery, but its AC power that's required by your critical loads, so this secondary conversion process is vital.

One of the main benefits of an online UPS is that it provides the greatest level of protection to your critical load from power 'events' such as spikes, sags, surges, electrical noise, and so on. This is because, unlike the other types of UPS described in our last article, all of the power supplied to your critical load has been routed through the UPS, and thus undergone the double conversion process from AC to DC and then back to AC.

### **Static Switch**

The switch has two modes; by default the switch will accept AC power from the UPS, but it also has the option to accept AC power directly from the mains, or 'bypass'.

Switching over to mains power is far from ideal, so in the event your critical loads are transferred to raw mains power it will be accompanied by an alarm or warning condition to ensure the UPS issue is resolved as quickly as possible.

### **Operation**:

- During normal or even abnormal line conditions, the inverter supplies energy from the mains through the rectifier, which charges the batteries continuously. In addition to that it can also provide power factor correction.

- When the line fails, the inverter still supplies energy to the loads from the batteries.

- As a consequence, no transfer time exists during the transition from normal to stored energy modes.

- In general, Online UPS system is the most reliable UPS configuration due to its simplicity (only three elements), and the continuous charge of the batteries, which means that they are always ready for the next power outage.

- This kind of UPS provides total independence between input and output voltage amplitude and frequency. So high output voltage quality can be obtained.

- When an overload occurs, the bypass switch connects the load directly to the utility mains, in order to guarantee the continuous supply of the load, thereby avoiding the damage to the UPS module (bypass operation).

- In this situation, the output voltage must be synchronized with the utility phase, otherwise the bypass operation will not be allowed.

- Typical efficiency of the online ups systems are up to 94%, which is limited due to the double conversion effect.

- Online UPS systems are typically used in environments with sensitive equipment or environments.

- Almost all commercial UPS units of 5 kVA and above are Online UPS Systems.

### 1.3.5Merits and demerits of online and off-line UPS

### Merits of on-line ups

- It provides isolation between main supply and load.

- Since inverter is always ON, the quality of load voltage is free from distortion

- All the disturbances of supply such as blackout, brownouts, spikes etc are absent in the output.

- Voltage regulation is better

- Transfer time is practically zero since inverter is always ON.

### Demerits of Online UPS:

- Overall efficiency of UPS is reduced since inverter is always ON.

- The wattage of the rectifier is increased since it has to supply power to inverter as well as charge battery

- Online UPS is costlier than other Uninterruptible Power Supply Systems.

### Applications of Online UPS:

- Induction motor drives and similar other motor control applications.

- Intensive care units, medical equipments.

### Merits of Offline UPS:

- Offline UPS has high efficiencies, since charger is not continuously on.

- The power handling capacity of charger is reduced.

- Offline UPS are not very costly.

- Internal control is simpler in offline Uninterruptible Power Supply.

### Demerits of Offline UPS:

- Since offline UPS provides mains supply when it is present, the output contains voltage spikes, brownouts, blackouts.

- There is finite transfer time from mains to inverter when mains supply fails.

- Output of offline Uninterruptible Power Supply is not perfectly reliable.

### **Applications of Offline UPS:**

- Computers, printers, scanners etc use offline UPS.

- Emergency power supplies, EPABX.

- •

### **1.3.6Need of Heat sink:**

The UPS carrier high current depending upon the load this current also flow throws the switching Device such as transistor, SCR used in the UPS.

They always heat up during operation since the electronic components are temperature dependent devices. The heat generated must be dissipated to the surroundings in order to keep the temperature within permissible limits. Generally these devices are fixed on a metal sheet (usually aluminum) so that additional heat is transferred to the aluminum sheet. The metal Sheet that serves to dissipate the additional heat from the power semi conductor devices is known as heat sink.

### **1.3.7Specification and Ratings**

| Sample Single Phase UPS Specification |                             |  |

|---------------------------------------|-----------------------------|--|

| UPS Output:                           | Specification               |  |

| Voltage                               | 220Vac                      |  |

| Frequency                             | 50Hz nominal, synchronized, |  |

| Power Rating                          | 1000VA                      |  |

| Load Power<br>Factor                  | 0.6                         |  |

| Load Crest<br>Factor                  | 3:1                         |  |

| Transfer Time                         | 5 milliseconds              |  |

| Current                               | 8.3 Amps                    |  |

| Overload<br>Capability                | 150%                        |  |

| Waveform                              | Sine-wave                   |  |

| Distortion                            | < 3% for non-linear loads   |  |

| UPS Input                             |                             |  |

| Voltage                               | 220V                        |  |

| Voltage Range                         | +10%, -15%                  |  |

| Frequency                  | 50Hz                                                   |

|----------------------------|--------------------------------------------------------|

| Maximum<br>Current         | 12.8 Amps                                              |

| Power Factor               | 0.9                                                    |

| UPS Battery                |                                                        |

| Туре                       | Sealed lead-acid, maintenance free                     |

| Rating                     | 12V, 7AH                                               |

| Number of<br>Cells         | 3                                                      |

| Diagnostics                | Periodic automatic test                                |

| Autonomy<br>Time           | 10 minutes at full load                                |

| Recharge Time              | 20 times the outage to 90% capacity.                   |

| Overall<br>System          |                                                        |

| Architecture               | Fault-tolerant, Double Conversion, On-Line,<br>Modular |

| Configuration              | Single-Phase Input and Output                          |

| Bypass                     | Automatic operation                                    |

| Efficiency                 | 85%                                                    |

| Operation                  | Fully Automatic or Manual Operation,                   |

| Control<br>Panel/Metering  | LED Display, Button Controls, No Metering              |

| Diagnostics &<br>Self Test | Self test on startup and periodically                  |

|                            |                                                        |

| Communications           |                                              |

|--------------------------|----------------------------------------------|

| User Interface           | RS232 port and Novell style contacts         |

| Networks                 | Via an Ethernet or Token Ring adapter        |

| SNMP                     | Via an SNMP adapter                          |

| Modem                    | Via a modem adapter                          |

| Mechanical               |                                              |

| Input                    | Hardwired                                    |

| Output                   | Hardwired                                    |

| Weight                   | 15.8 kg (35 lbs)                             |

| Dimensions<br>(LxWxH)    | 499 x 134 x 226 mm (19.6 x 5.3 x 8.9 inches) |

| Environmental            |                                              |

| Audible Noise            | < 50 dBA                                     |

| Operating<br>Temperature | 30°c                                         |

| Storage<br>Temperature   | - 20°c                                       |

| Relative Humidity        | 5 - 95% non-condensing                       |

| Altitude                 | 1000m without derating                       |

| Safety                   | UL 1778                                      |

| EMC - Emissions          | FCC Class A                                  |

| EMC - Immunity           | Not Applicable                               |

| Surge<br>Suppression     | IEEE 587 (ANSI C62.41)                       |

| CMNR                     | > 60dB                                       |

| TMNR          | > 80dB                                              |

|---------------|-----------------------------------------------------|

| Packaging     | No CFC's, Recyclable                                |

| Options       |                                                     |

| Battery Packs | Battery Modules and special long autonomy solutions |

# **UPS Output Specifications**

| Voltage                 | The UPS output voltage must match the requirement of the load. In North America this voltage is 120Vac, in most of Europe 230Vac is used and the rest of the world is 220Vac.                                                                                                                             |  |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Regulation              | The regulation specification is the maximum expected deviation for the normal output voltage (e.g. 220Vac) that is expected over the entire range of operating conditions (e.g. load, temperature, altitude). For Off-Line systems the regulation spec refers to the battery backup mode.                 |  |

| Frequency               | The frequency of the UPS output must match the requirements of the load. Switch-mode power supplies have a wide (47 - 63 Hz) range to be able to operate from either 50 or 60Hz. Other loads may require either 50 or 60Hz.                                                                               |  |

| Power<br>Rating         | To completely specify a UPS, both the Volt-Ampere (VA) and wattage (Watts) rating must be known. See the section on "Understanding Watts, VA and Power Factor" for an in-depth explanation.                                                                                                               |  |

| Load<br>Power<br>Factor | A power factor (p.f.) in the 0.6 to 0.8 range is typical. A p.f. rating of 0.6 to 0.7 is good for a switch-mode power supply. A p.f of 0.8 is typical for older UPS equipment designs used before the widespread use of computers.                                                                        |  |

|                         |                                                                                                                                                                                                                                                                                                           |  |

| Load Crest<br>Factor    | Most loads used in modern equipment, including computers, require a peak<br>current that is much higher than what is required by a simple load such as a<br>light bulb. The UPS must be able to supply this peak current. The Load<br>Crest Factor is the ratio of the peak to the average (RMS) current. |  |

| Transfer<br>Time                | In an On-Line system the transfer time refers to a change from the bypass source to the UPS and vice-versa. A typical time is ¼ of a cycle or about 5-6 milliseconds.                                           |  |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                 | In an Off-Line system the transfer time refers to the change from the utility source to the inverter when there is a power outage and is about 5 to 10 milliseconds.                                            |  |

| Current                         | The output current refers to the maximum current available at the normal output voltage.                                                                                                                        |  |

| Overload<br>Capability          | If more loads is added to a UPS and the new total is more than the rating, the UPS must be able to continue to function. At typical Overload specification is 1.25% for 10 minutes or 150% for 1 minute.        |  |

| Wavef<br>orm                    | Not all UPS products have a sine-wave output and most modern loads do<br>not require a perfect sine-wave source. Lower cost UPS equipment will have<br>a quasi square-wave or a step sine-wave output waveform. |  |

| Distor<br>tion                  | If the UPS has a sine-wave output a distortion figure indicates how good the wave shape is. A typical distortion value is 3% for linear loads and 5% for non-linear load.                                       |  |

| Transi<br>ent<br>Regul<br>ation | ent maximum amount the output voltage deviates from the nominal valu indicates the transient regulation. If the voltage deviates too much, som                                                                  |  |

# **UPS Input Specifications**

| Voltage            | The input voltage specification is the nominal voltage the UPS expects to see on its input.                                                                                     |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Voltage<br>Range   | All UPS products are designed to operate over a range of input voltages. A typical range is +10% to - 15% or 102Vac to 132Vac for North America or 196Vac to 253Vac for Europe. |

| Frequency          | Modern UPS equipment will operate on either 50 or 60Hz as long as the voltage is within the specified limits. Some UPS equipment is designed to operate only on 50 or 60Hz.     |

| Maximum<br>Current | The maximum current occurs when the UPS is fully loaded and the input voltage is at the minimum                                                                                 |

|                 | allowed for normal operation (usually about -15%).                                                                                                                                                                                                                                                                                                                                                                                              |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power<br>Factor | The UPS input is a load on the utility power source.<br>The UPS input power factor (p.f.) varies with how<br>much load is on the output of the UPS and in<br>modern UPS equipment is 0.9 or better. In large<br>UPS equipment (e.g. 25kVA) the input power factor<br>could be a very important part of the overall system<br>design. In small UPS equipment, power factor is<br>usually not a concern unless many units are being<br>installed. |

# **UPS Battery Specifications**

| Туре            | The most common battery used in UPS<br>equipment is a sealed, lead-acid,<br>maintenance free type. Ni-Cad (Nickel-<br>Cadmium) batteries are a more expensive<br>option. Large UPS systems often use wet,<br>lead-acid storage batteries. |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rating          | Batteries are rated by specifying an open circuit DC voltage and a Ampere-Hour (AH) rating.                                                                                                                                               |

| Number of Cells | Battery cells are normally connected in series to form a string. Often battery strings are connected in parallel.                                                                                                                         |

| Diagnostics     | The battery is the weakest link in a UPS system. Automatic checking and diagnostics of battery problems is now common in UPS products. Testing must not put the load in jeopardy.                                                         |

# 1.3.8Maintenance of UPS including batteries

Regular equipment testing should be part of a facility's UPS maintenance schedule. Such a schedule might include the following elements:

# Quarterly:

• Visually inspect equipment for loose connections, burned insulation or any other signs of wear.

# Semiannually:

Visually check for liquid contamination from batteries and capacitors.

Clean and vacuum UPS equipment enclosures.

Check HVAC equipment and performance related to temperature and humidity.

# Annually:

Conduct thermal scans on electrical connections to ensure all are tight and not generating heat, which is the first and sometimes only indication of a problem. A non-evasive diagnostic tool helps technicians identify hot spots invisible to the human eye. Technicians should retorque if thermal scan provides evidence of a loose connection.

Provide a complete operational test of the system, including a monitored battery-rundown test to determine if any battery strings or cells are near the end of their useful lives.

# **Biannually:**

• Test UPS transfer switches, circuit breakers and maintenance bypasses.

# UNIT II TRANSFORMER AND SPECIAL MOTORS

# **OBJECTIVES:**

- > Understand the concept of transformer

- > Know the working and parts of a transformer

- > Know about the stepper motors and servo motors

- Know the electrical safety

# 2.1.1 Single phase Transformer

# **Definition of Transformer**

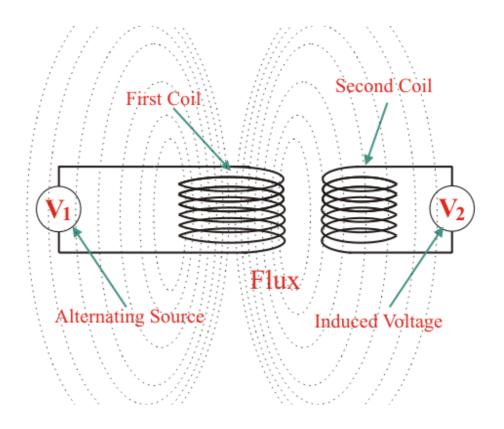

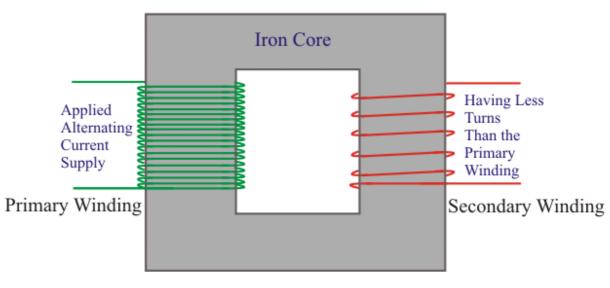

Electrical power transformer is a static device which transforms electrical energy from one circuit to another without any direct electrical connection and with the help of mutual induction between two windings. It transforms power from one circuit to another without changing its frequency but may be in different voltage level.

This is a very short and simple definition of transformer,

# 2.1.2Working Principle of Transformer

The **working principle of transformer** is very simple. It depends upon **Faraday's law of electromagnetic induction**. Actually, mutual induction between two or more winding is responsible for transformation action in an electrical transformer.

# Faraday's Laws of Electromagnetic Induction

According to these Faraday's laws,

"Rate of change of flux linkage with respect to time is directly proportional to the induced EMF in a conductor or coil".

# **Basic Theory of Transformer**

Say you have one winding which is supplied by an alternating electrical source. The alternating current through the winding produces a continually changing flux or alternating flux that surrounds the winding. If any other winding is brought nearer to the previous one, obviously some portion of this flux will link with the second. As this flux is continually changing in its amplitude and direction, there must be a change in flux linkage in the second winding or coil. According to **Faraday's Laws of Electromagnetic Induction**

, there must be an EMF induced in the second. If the circuit of the later winding is closed, there must be an current flowing through it. This is the simplest form of electrical power transformer and this is the most basic of **working principle of transformer**.

For better understanding, we are trying to repeat the above explanation in a more brief way here. Whenever we apply alternating current to an electric coil, there will be an alternating flux surrounding that coil. Now if we bring another coil near the first one, there will be an alternating flux linkage with that second coil. As the flux is alternating, there will be obviously a rate of change in flux linkage with respect to time in the second coil. Naturally emf will be induced in it as per **Faraday's Laws of Electromagnetic Induction**

. This is the most basic concept of the theory of transformer.

The winding which takes electrical power from the source, is generally known as primary winding of transformer. Here in our above example it is first winding.

The winding which gives the desired output voltage due to mutual induction in the transformer, is commonly known as secondary winding of transformer. Here in our example it is second winding.

The above mentioned form of transformer is theoretically possible but not practically, because in open air very tiny portion of the flux of the first winding will link with second; so the current that flows through the closed circuit of later, will be so small in amount that it will be difficult to measure.

The rate of change of flux linkage depends upon the amount of linked flux with the second winding. So, it is desired to be linked to almost all flux of primary winding to the secondary winding. This is effectively and efficiently done by placing one low reluctance path common to both of the winding. This low reluctance path is core of transformer, through which maximum number of flux produced by the primary is passed through and linked with the secondary winding. This is the most basic **theory of transformer**. In short, a transformer carries the operations shown below:

Transfer of electric power from one circuit to another.

Transfer of electric power without any change in frequency.

Transfer with the principle of electromagnetic induction.

The two electrical circuits are linked by mutual induction

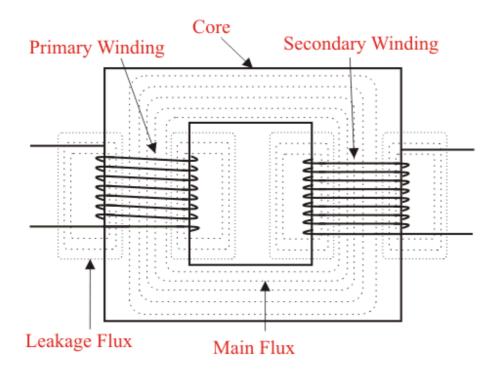

# 2.1.3 Main Constructional Parts of Transformer

The three main parts of a transformer are,

# 1. Primary Winding of Transformer-

Which produces magnetic flux when it is connected to electrical source.

### 2. Magnetic Core of Transformer-

The magnetic flux produced by the primary winding, that will pass through this low reluctance path linked with secondary winding and create a closed magnetic circuit.

# 3. Secondary Winding of Transformer-

The flux, produced by primary winding, passes through the core, will link with the secondary winding. This winding also wounds on the same core and gives the desired output of the **transformer**

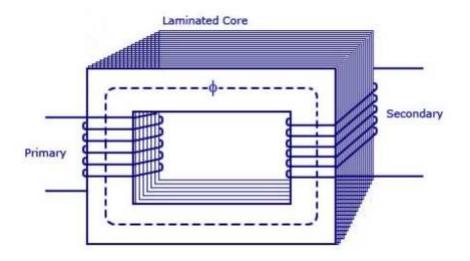

Two coils of wire (called windings) are wound on some type of core material. In some cases the coils of wire are wound on a cylindrical or rectangular cardboard form. In effect, the core material is air and the transformer is called an **AIR-CORE TRANSFORMER**.

Transformers used at low frequencies, such as 60 hertz and 400 hertz, require a core of low-reluctance magnetic material, usually iron. This type of transformer is called an **IRON-CORE TRANSFORMER**. Most power transformers are of the iron-core type.

The ENCLOSURE, which protects the above components from dirt, moisture, and

Mechanical damage

2.1.4Brief description of each part

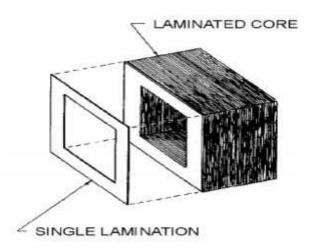

(i)CORE

There are two main shapes of cores used in laminated-steel-core transformers. One is the HOLLOWCORE, so named because the core is shaped with a hollow square through the center. This shape of core. Notice that the core is made up of many laminations of steel it shows how the transformer windings are wrapped around both sides of the core.

- \* The core is made up of silicon steel laminated iron core

- \* The steel cores are varnished and insulated

- \* Thickness of lamination is from 0.35 to 0.5 MM

- \* The eddy current loss is minimized by laminated core

- \* The core is made up of silicon steel so, hysteresis loss is reduced

- \* Core has different shape E I L

- \* All the sheets are joined together tightly by bolt

- \* Small transformer are rectangle in shape. big transformers are square in shape

#### (ii) WINDINGS

As stated above, the transformer consists of two coils called WINDINGS which are wrapped around a core. The transformer operates when a source of ac voltage is connected to one of the windings and a load device is connected to the other. The winding that is connected to the source is called the PRIMARY WINDING. The winding that is connected to the load is called the SECONDARY WINDING. The primary is wound in layers directly on a rectangular cardboard form.

#### 2.1.5EMF Equation of Transformer:

Let the applied voltage V<sub>1</sub> applied to the primary of a transformer, with secondary opencircuited, be sinusoidal (or sine wave). Then the current I<sub>1</sub>, due to applied voltage V<sub>1</sub>, will also be a sine wave. The mmf, N<sub>1</sub> x I<sub>1</sub> and core flux Ø will follow the variations of I<sub>1</sub> closely. That is the flux is in time phase with the current I<sub>1</sub> and varies sinusoidally.

Let,

$N_1$  = Number of turns in primary

N<sub>2</sub>= Number of turns in secondary

$Ø_{max}$  = Maximum flux in the core in webers =  $B_{max} X A f$  = Frequency of alternating current input in hertz (H<sub>z</sub>)

As shown in figure above, the core flux increases from its zero value to maximum value  $Ø_{max}$  in one quarter of the cycle , that is in  $\frac{1}{4}$  frequency second.

Therefore, average rate of change of flux =  $\mathcal{Q}_{max}/\frac{1}{4} \mathbf{f} = 4\mathbf{f} \mathcal{Q}_{max}$ Wb/s

Now, rate of change of flux per turn means induced electro motive force in volts. Therefore,

Average electro-motive force induced/turn = 4f  $Ø_{max}$ volt

If flux Ø varies sinusoidally, then r.m.s value of induced e.m.f is obtained by multiplying the average value with form factor.

Form Factor = r.m.s. value/average value = 1.11 Therefore, r.m.s value of e.m.f/turn = 1.11 X 4f  $Ø_{max}$  = 4.44f  $Ø_{max}$ Now, r.m.s value of induced e.m.f in the whole of primary winding = (induced e.m.f./turn) X Number of primary turns

Therefore,

$E_1 = 4.44f N_1 \varnothing_{max} = 4.44f N_1 B_m A$ Similarly, r.m.s value of induced e.m.f in secondary is  $E_2 = 4.44f N_2 \varnothing_{max} = 4.44f N_2 B_m A$ In an ideal transformer on no load  $V_1 = E_1$  and  $V_2 = E_2$

In an ideal transformer on no load,  $V_1$  =  $E_1$  and  $V_2$  =  $E_2,$  where  $V_2$  is the terminal voltage

# 2.1.6Voltage and current ratio of a transformer **Voltage Transformation Ratio.**

The ratio of secondary voltage to primary voltage is known as the voltage transformation ratio and is designated by letter K. i.e.

Voltage transformation ratio,  $\mathbf{K} = \mathbf{V}_2/\mathbf{V}_1 = \mathbf{E}_2/\mathbf{E}_1 = \mathbf{N}_2/\mathbf{N}_1$

# **Current Transformation Ratio.**

The ratio of secondary current to primary current is known as current ratio and is reciprocal of voltage transformation ratio in an ideal transformer. Current transformation ratio, =  $I_2/I_1 = N_1/N_2 = 1/K$

#### **Transformation Ratio of Transformer**

The constant K is called transformation ratio of transformer,

If  $T_2 > T_1$ , K > 1, then the transformer is step up transformer. If  $T_2 < T_1$ , K < 1, then the transformer is step down transformer.

# **Turns Ratio of Transformer**

As the voltage in primary and secondary of transformer is directly proportional to the number of turns in the respective winding, the transformation ratio of transformer is sometime expressed in ratio of turns and referred as turns ratio of transformer. 2.1.7Efficiency

Efficiency of a transformer is defined as ratio of output power to input power Efficiency=(output power/input power)\*100=(output power/(output+losses))\*100 Efficiency of the transformer is more than 99%.

- 2.1.8Losses in a Transformer

- 1. Copper loss or Variable loss

- 2. Core losses or iron loss or constant loss

- 1. Copper Loss in Transformer

Copper loss is I<sup>2</sup>R loss, in primary side it is  $I_1^2R_1$  and in secondary side it is  $I_2^2R_2$  loss, where  $I_1$  and  $I_2$  are primary and secondary current of transformer and  $R_1$  and R<sub>2</sub> are resistances of primary and secondary winding. As the both primary & secondary currents depend upon load of transformer, copper loss in transformer vary with load.

# 2. Core Losses in Transformer

Hysteresis loss and eddy current loss both depend upon magnetic properties of the materials used to construct the core of transformer and its design. So these losses in transformer are fixed and do not depend upon the load current. So core losses in transformer which is alternatively known as iron loss in transformer can be considered constant for load. as all range Hysteresis loss in transformer is denoted as,  $W_h = K_h f(B_m)^{1.6}$  watts

Eddy current loss in transformer is denoted as ,  $W_e = K_e f^2 K_f^2 B_m^2 watts$ Where K<sub>b</sub>=Hysteresis constant

# 2.1.9Auto Transformer

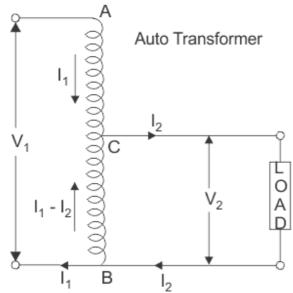

Auto transformer is kind of electrical transformer where primary and secondary shares same common single winding. So basically it's a one winding transformer.

#### **Theory of Auto Transformer**

In Auto Transformer, one single winding is used as primary winding as well as secondary winding. But in two windings transformer two different windings are used for primary and secondary purpose. A diagram of auto transformer is shown above. The winding AB of total turns N<sub>1</sub> is considered as primary winding. This winding is tapped from point 'C' and the portion BC is considered as secondary. Let's assume the number of turns in between points 'B' and 'C' is N<sub>2</sub>.

If  $V_1$  voltage is applied across the winding i.e. in between 'A' and 'C'.

So voltage per turn in this winding is  $\frac{V_1}{N_2}$

Hence, the voltage across the portion BC of the winding, will be,

$\frac{V_1}{N_1}XN_2$  and from the figure above, this voltage is  $V_2$

Hence,

$$\frac{V_1}{N_1}XN_2 = V_2$$

$\Rightarrow \frac{V_2}{V_1} = \frac{N_2}{N_1} = Constant = K$

As BC portion of the winding is considered as secondary, it can easily be understood that value of constant 'k' is nothing but turns ratio or voltage ratio of that **auto transformer**. When load is connected between secondary terminals i.e. between 'B' and 'C', load current  $I_2$  starts flowing. The current in the secondary winding or common winding is the difference of  $I_2 \& I_1$ .

Auto transformer employs only single winding per phase as against two distinctly separate windings in a conventional transformer.

#### 2.1.10Comparison with two winding Transformers

I).For transformation ratio = 2, the size of the **auto transformer** would be approximately 50% of the corresponding size of two winding transformer. For transformation ratio say 20 however the size would be 95 %. The saving in cost of the material is of course not in the same proportion. The saving of cost is appreciable when the ratio of transformer is low, that is lower than 2. Thus auto transformer is smaller in size and cheaper.

II).An auto transformer has higher efficiency than two winding transformer. This is because of less ohmic loss and core loss due to reduction of transformer material.

III).Auto transformer has better voltage regulation as voltage drop in resistance and reactance of the single winding is less.

#### **Disadvantages of Using Auto Transformer**

I).Because of electrical conductivity of the primary and secondary windings the lower voltage circuit is liable to be impressed upon by higher voltage. To avoid breakdown in the lower voltage circuit, it becomes necessary to design the low voltage circuit to withstand higher voltage.

II). The leakage flux between the primary and secondary windings is small and hence the impedance is low. This results into severer short circuit currents under fault conditions.

III). The connections on primary and secondary sides have necessarily needs to be same, except when using interconnected starring connections. This introduces complications due to changing primary and secondary phase angle particularly in the case of delta/delta connection.

IV).Because of common neutral in a star/star connected auto transformer it is not possible to earth neutral of one side only. Both their sides should have their neutrality either earth or isolated.

V).It is more difficult to maintain the electromagnetic balance of the winding when voltage adjustment tapping are provided. It should be known that the provision of tapping on an auto transformer increases considerably the frame size of the transformer. If the range of tapping is very large, the advantages gained in initial cost is lost to a great event.

# 2.1.11Applications of Auto Transformers

1. Compensating voltage drops by boosting supply voltage in distribution systems.

2. Auto transformers with a number of tapping are used for starting induction and synchronous motors.

**3.** Auto transformer is used as variac in laboratory or where continuous variable over broad ranges are required.

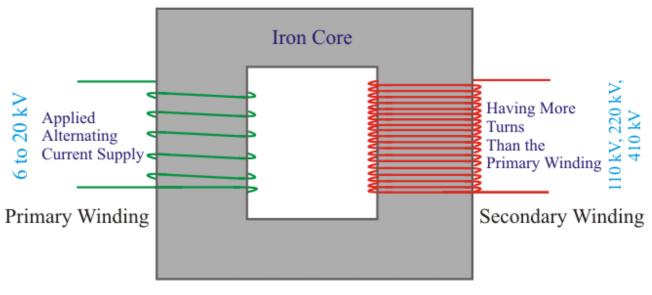

### 2.1.12Step up and step down transformer

With those features, the transformer is the most important part of the electrical system and provides economical and reliable transmission and distribution of electrical energy. The transformer can transfer energy in both directions, from HV to LV side as well as inversely. That is the reason why it can work as voltage step up or step down transformer. Both transformer types have the same design and construction. Any transformer can operate as step-up or step-down type. It is only depending on the energy flows direction.

# Step up transformer

Step Up Transformer

The primary side of a **step-up transformer** has a small number of turns (LV side) while the transformer secondary side has many number of turns (HV side). That means an energy flows from the LV to HV side.

. Those transformers usually have large turns ratio value.

# Applications of step up transformer

The small **step-up transformers** can be used in electronic and electrical devices where the voltage boosting is required. But nowadays in the modern electronic device, power electronic circuits are more frequently used because of weight and dimension.

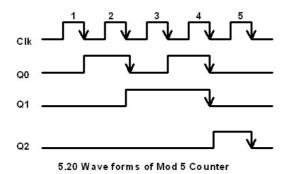

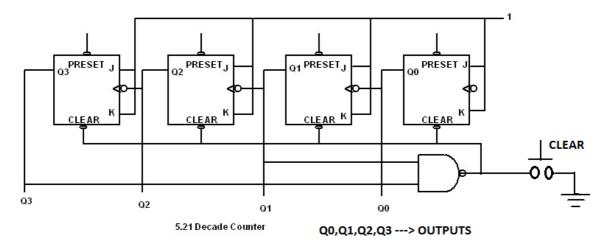

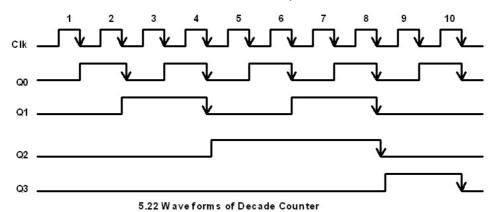

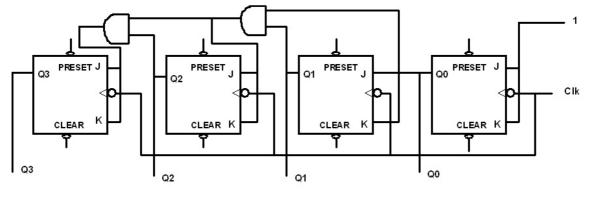

# Step down transformer